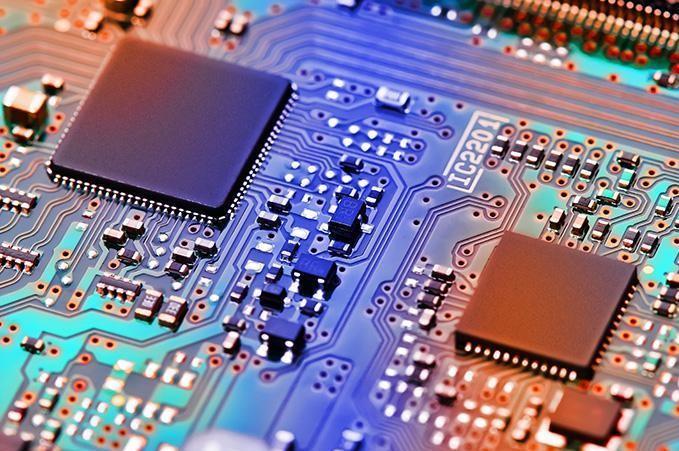

Title: Part No. X28C64JM-20

Introduction:

The X28HC256 is a third-generation or high-performance CMOS 32K x 8 E2PROM. It is fabricated with Xicor’s intercession, textured, or indulge in poly floating gate technology providing a highly reliable 5 Volt only nonvolatile memory not volatile. The X28C64JM-20 provisions a 128-byte page write process, effectively providing a 25µs/byte write cycle and enabling the whole memory to be usually rewritten in less than 0.8 seconds. The X28C64JM-20 also showcases DATA Polling and Toggle Bit Polling, two methods of offering early end of write detection. The X28C64JM-20 also supports the JEDEC specification Software Data Protection feature for protective against involuntary writes for the duration of power-up and power-down.

Features:

65 ns access time

Page write and simple byte

CMOS is low power up to some extent

Write detection is early end

Working:

The EEPROM uses the principle or main aim same as that of the UV-EPROM. The electrons which are trapped or in between there in a floating gate of ROM will modify or change the parameters of the cell, so instead of that logic “Zero” or logic “One” will be stored or present. EEPROM is the memory device which implements or implanted the fewest or standards in cell design of memory. Most of the common or ordinary cells are composed of two transistors. In this the store charge transistor has the floating gate that will trap the electrons. Apart from that there is an admittance to the transistor which is used in the procedure. In EPROM, cell is removed or finished when electrons are eliminated from the floating gate or at last end stage, but in EEPROM, cell is erased when electrons are entrapped or in between the floating cell.

Applications:

Used in computers

Laptops

In latest mobile technologies

In latest tablets

In LEDs